# SAMSUNG SEMICONDUCTOR INC 02 DE 7964142 0006499 3

## KS54HCTLS 373 KS74HCTLS

with 3-State Outputs

Octal D-Type Transparent Latches

#### FEATURES

- 8 latches in a single package

Full parallel access for loading

- Function, pin-out, speed and drive compatibility with 54/74LS logic family

- Low power consumption characteristic of CMOS

- 3-State outputs with high drive current

- (I<sub>OL</sub> = 24 mA @ V<sub>OL</sub> = 0.5V) for direct bus interface • Inputs and outputs interface directly with TTL, NMOS and CMOS devices

- Wide operating voltage range: 4.5V to 5.5V

- Characterized for operation over industrial and

- military temperature ranges:

- KS74HCTLS: -40°C to +85°C

- KS54HCTLS: -55°C to +125°C Package options include plastic "small outline"

- packages, standard plastic and ceramic 300-mil DIPs

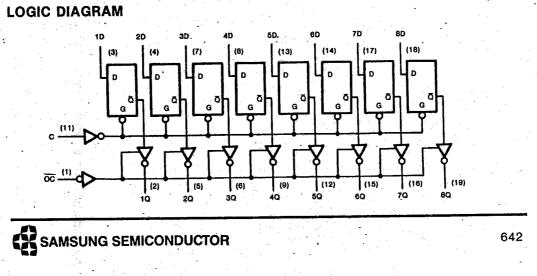

### PIN CONFIGURATION

### DESCRIPTION

The '373 consists of 8 high-speed D-type latches coupled to 3-state output buffers with high drive current capability. It can be used in implementing buffer registers, I/O ports, bidirectional bus drivers and working registers.

T-46-07-05

The latches are transparent: when the enable (C) is high, the Q outputs follow the data (D) inputs. When the enable is low, the outputs latch at the levels that were set up at the D inputs.

The output buffers are controlled by a common signal ( $\overline{OC}$ ) which places the outputs at a high-impedance state when it is taken high. The  $\overline{OC}$  signal does not affect the internal operations of the latches. Old data can be retained or new data can be entered while outputs are off.

These devices provide speeds and drive capability equivalent to their LSTTL counterparts and yet maintain CMOS power levels. The input and output voltage levels allow direct interface with TTL, NMOS and CMOS devices without any external components.

All inputs and outputs are protected from damage due to static discharge by internal diode clamps to Vcc and ground.

### **FUNCTION TABLE**

| ,<br>I | (Each    | Latch) |                 |  |

|--------|----------|--------|-----------------|--|

|        | Inputs   |        | Output          |  |

| ŌC     | Enable C | D      | Q               |  |

| L      | н        | н      | H               |  |

| L      | Н        | E.     | L               |  |

| L      | L T      | · X    | .Q <sub>0</sub> |  |

| н      | X        | X      | z               |  |

# SAMSUNG SEMICONDUCTOR INC DE 7964142 0006500 6

# KS54HCTLS 373 KS74HCTLS

#### **Absolute Maximum Ratings\***

Supply Voltage Range Vcc. -0.5V to +7V DC Input Diode Current,  $I_{IK}$ (V<sub>I</sub> < -0.5V or V<sub>L</sub> > V<sub>CC</sub> +0.5V) .... ±20 mA DC Output Diode Current, lox

$(V_0 < -0.5V \text{ or } V_0 > V_{CC} + 0.5V) \dots \pm 20 \text{ mA}$

Continuous Output Current Per Pin,  $1_0$ (-0.5V < V<sub>0</sub> < V<sub>CC</sub> +0.5V) .....  $\pm$ 70 mA Continuous Current Through

Absolute Maximum Ratings are those values beyond which permanent damage to the device may occur. These are stress ratings only and functional operation of the device at or beyond them is not implied. Long exposure to these conditions may affect device reliability. Power Dissipation temperature derating: Plastic Package (N): - 12mW/°C from 65°C to 85°C Ceramic Package (J): -12mW/°C from 100°C to 125°C

Octal D-Type Transparent Latches

with 3-State Outputs T-46-07-05

#### **Recommended Operating Conditions**

Range

KS74HCTLS:

-40°C to

+85°C

KS54HCTLS:

-55°C to

+125°C

voltage level (either V<sub>CC</sub> or GND)

| Characteristic                             | Symbol | Test Conditions                                                                                                             | T <sub>A</sub> =25°C   |                              | KS74HCTLS<br>$T_A = -40$ °C to $+85$ °C | KS54HCTLS<br>T <sub>A</sub> = -55°C to +125°C | Unit     |

|--------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------|-----------------------------------------|-----------------------------------------------|----------|

|                                            |        |                                                                                                                             | Тур                    |                              | Guaranteed Lim                          | its                                           | <u> </u> |

| Minimum High-Level<br>Input Voltage        | VIH    |                                                                                                                             |                        | 2.0                          | 2.0                                     | 2,0                                           | V        |

| Maximum Low-Level<br>Input Voltage         | ViL    |                                                                                                                             | -                      | 0.8                          | 0.8                                     | 0.8                                           | v        |

| Minimum High-Level<br>Output Voltage       | Vон    | $V_{IN} = V_{IH} \text{ or } V_{IL}$<br>$I_0 = -20\mu A$<br>$I_0 = -6m A$                                                   | V <sub>CC</sub><br>4.2 | V <sub>CC</sub> -0,1<br>3.98 | V <sub>CC</sub> -0.1<br>3.84            | V <sub>CC</sub> -0.1<br>3.7                   | v        |

| Maximum Low-Level<br>Output Voltage        | VoL    | V <sub>IN</sub> =V <sub>IH</sub> or V <sub>IL</sub><br>I <sub>O</sub> =20µA<br>I <sub>O</sub> =12mA<br>I <sub>O</sub> =24mA | 0                      | 0.1<br>0.26<br>0.39          | 0.1<br>0.33<br>0.5                      | 0.1<br>0.4                                    | v        |

| Maximum Input<br>Current                   | lın    | V <sub>IN</sub> =V <sub>CC</sub> or GND                                                                                     |                        | ±0.1                         | ±1.0'                                   | ±1.0                                          | μA       |

| Maximum 3-State<br>Leakage Current         | loz    | Output Enable<br>=V <sub>IH</sub><br>V <sub>OUT</sub> =Vcc or GND                                                           |                        | ±0.5                         | ±5.0                                    | ±10.0                                         | μA       |

| Maximum Quiescent<br>Supply Current        | lcc    | V <sub>IN</sub> =V <sub>CC</sub> or GND<br>I <sub>OUT</sub> =0µA                                                            | -                      | 8.0                          | 80.0                                    | 160.0                                         | μA       |

| Additional Worst<br>Case Supply<br>Current | Δlcc   | per input pin<br>$V_Z=2.4V$<br>Other inputs:<br>At $V_{CC}$ or GND<br>$I_O=0$                                               |                        | 2.7                          | 2.9                                     | 3.0                                           | mA       |

#### DC ELECTRICAL CHARACTERISTICS (Vcc=5V±10% Unless Otherwise Specified)

| AC | <b>ELECTRICAL</b> | CHARACTERISTICS (Input tr, tr<6 ns), HCTLS: | 373 |

|----|-------------------|---------------------------------------------|-----|

|    |                   |                                             |     |

| Characteristic                                | Symbol           | Cendlilons                                    |                                 | T <sub>a</sub> = 25°C<br>V <sub>CC</sub> = 5.0V |          | K\$74HCTLS<br>$\tilde{T}_{s} = -40^{\circ}C \text{ to } +85^{\circ}C$<br>$V_{CC} = 5.0V \pm 10\%$ | KS54HCTLS<br>$T_a = -55^{\circ}C \text{ to } +125^{\circ}C$<br>$V_{CC} = 5.0V \pm 10\%$ | Unit |

|-----------------------------------------------|------------------|-----------------------------------------------|---------------------------------|-------------------------------------------------|----------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------|

|                                               |                  |                                               |                                 | Тур                                             |          | Guarantee                                                                                         | d Limite                                                                                | 1.1  |

| *<br>Maximum Propagation Delay,               | фин              | CL= 50pF<br>CL=150pF                          |                                 | 14<br>17                                        | 18<br>21 | 23<br>28                                                                                          | 27<br>33                                                                                | ns   |

| D to Q                                        | <b>t</b> PHL     | C <sub>L</sub> =50pl<br>C <sub>L</sub> =150   | 14<br>17                        | 18<br>21                                        | 23<br>28 | 27<br>33                                                                                          |                                                                                         |      |

| Maximum Propagation Delay,<br>C to any Q      | <b>t</b> PLH     | C <sub>L</sub> ≕50pF<br>C <sub>L</sub> ≕150pF |                                 | 22<br>25                                        | 30<br>33 | 37<br>42                                                                                          | 45<br>51                                                                                | ns   |

|                                               | <b>t</b> PHL     | C <sub>L</sub> =50pl<br>C <sub>L</sub> =150   |                                 | 22<br>25                                        | 30<br>33 | 37<br>42                                                                                          | 45<br>51                                                                                |      |

| Maximum Output Enable<br>Time, OC to any Q    | tpz <sub>H</sub> | -BL=1kΩ                                       | CL=50pF<br>CL=150pF             | 24<br>27                                        | 32<br>35 | 40<br>45                                                                                          | 48<br>54                                                                                | - ns |

|                                               | t <sub>PZL</sub> |                                               | $C_L = 50 pF$<br>$C_L = 150 pF$ | 24<br>27                                        | 32<br>35 | 40<br>45                                                                                          | . 48<br>54                                                                              |      |

| Maximum Output Disable<br>Time, OC to any Q   | t <sub>PHZ</sub> | R <sub>L</sub> =1kΩ<br>C <sub>L</sub> =50p    | 19<br>19                        | 25<br>25                                        | 31<br>31 | 37<br>37                                                                                          | ns                                                                                      |      |

| Minimum Pulse Width,<br>C High                | ťw               |                                               |                                 | 6                                               | 10       | 12                                                                                                | 15                                                                                      | ns   |

| Minimum Setup Time,<br>D before CI            | tsu              |                                               |                                 | 2                                               | 3        | 4                                                                                                 | 5                                                                                       | ns   |

| Minimum Hold Time,<br>D after CI              | th               |                                               |                                 | 6                                               | 10       | 12                                                                                                | 15                                                                                      | ns   |

| Maximum Input Capacitance                     | CiN              |                                               |                                 | 5                                               |          |                                                                                                   |                                                                                         | pF   |

| Maximum Output Capacifance                    | COUT             | Output D                                      | isabled                         | 10                                              |          |                                                                                                   |                                                                                         | pF   |

| Power Dissipation<br>Capacitance* (per latch) | CPD              | OC=Vcc<br>OC=GN                               | D                               | 5<br>30                                         |          |                                                                                                   |                                                                                         | pF   |

\* CPD determines the no-load dynamic power dissipation: PD=CPD Vcc<sup>2</sup> f + lcc Vcc. † For AC switching test circuits and timing waveforms see section 2.

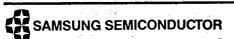

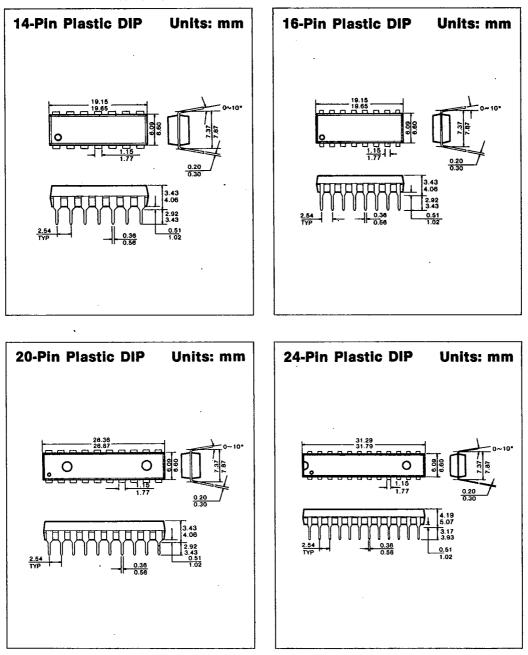

### PACKAGE DIMENSIONS

T-90-20

. . . .

٠

### **1. PLASTIC PACKAGES**

SAMSUNG SEMICONDUCTOR

781

PACKAGE DIMENSIONS

1

T-90-20

SAMSUNG SEMICONDUCTOR 782 1676 A-05

Download from www.ICminer.com Electronic-Library Service

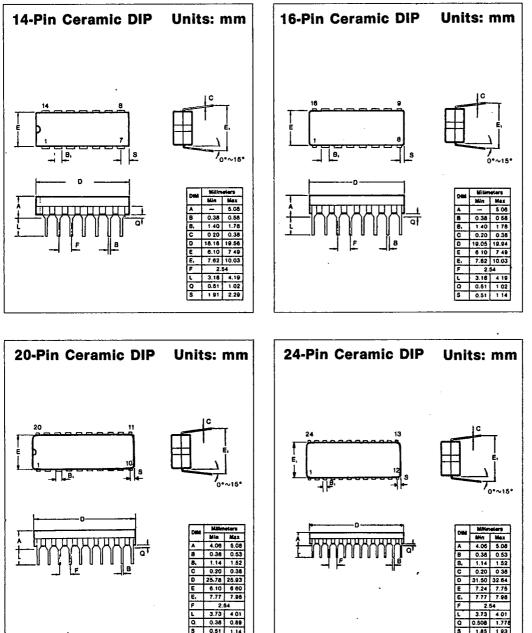

## PACKAGE DIMENSIONS

T-90-20

#### 2. CERAMIC PACKAGES

.

. .

SAMSUNG SEMICONDUCTOR